Home Search Collections Journals About Contact us My IOPscience

### Effect of improved contact on reliability of sub-60 nm carbon nanotube vias

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2016 Nanotechnology 27 375202

(http://iopscience.iop.org/0957-4484/27/37/375202)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 152.135.235.188

This content was downloaded on 03/08/2016 at 17:37

Please note that terms and conditions apply.

IOP Publishing Nanotechnology

Nanotechnology 27 (2016) 375202 (11pp)

doi:10.1088/0957-4484/27/37/375202

# Effect of improved contact on reliability of sub-60nm carbon nanotube vias

## Anshul A Vyas<sup>1</sup>, Changjian Zhou<sup>2</sup>, Yang Chai<sup>2</sup>, Phillip Wang<sup>3</sup> and Cary Y Yang<sup>1</sup>

- <sup>1</sup> Center for Nanostructures, Santa Clara University, Santa Clara, CA, USA

- <sup>2</sup> Department of Applied Physics, Hong Kong Polytechnic University, Hung Hom, Hong Kong

- <sup>3</sup> Applied Materials Inc., Sunnyvale, CA, USA

E-mail: AVyas@scu.edu

Received 4 April 2016, revised 23 May 2016 Accepted for publication 2 June 2016 Published 3 August 2016

#### **Abstract**

Advances in semiconductor technology due to the aggressive downward scaling of on-chip feature sizes have led to rapid rises in the resistivity and current density of interconnect conductors. As a result, current interconnect materials, Cu and W, are subject to performance and reliability constraints approaching or exceeding their physical limits. Therefore, alternative materials are being actively considered as potential replacements to meet such constraints. The carbon nanotube (CNT) is among the leading replacement candidates for on-chip interconnect vias due to its high aspect-ratio nanostructure and superior current-carrying capacity to Cu and W, as well as other potential candidates. Based on the results for 40 nm and 60 nm top-contact metallized CNT vias, we demonstrate that not only are their current-carrying capacities two orders of magnitude higher than their Cu and W counterparts, they are enhanced by reduced via resistance due to contact engineering facilitated by the first reported contact resistance extraction scheme for a 40 nm linewidth.

Keywords: carbon nanotubes, contact resistance, metallization, interconnects, current-carrying capacity

1

(Some figures may appear in colour only in the online journal)

#### 1. Introduction

For the past two decades, there have been unprecedented advances in semiconductor technology, guided by Moore's law and engineered by lithography-based scaling [1]. This has resulted in the aggressive downsizing of on-chip components such as transistors (active devices or front-end-of-line) and interconnects (passive devices or middle-of-line and backend-of-line) [2]. Scaling transistor dimensions result in a reduction of the areas of gate capacitors and other parasitic capacitors. This enables transistors to operate with smaller voltage swings and faster charge/discharge or switching cycles. Therefore, scaling transistors improve their performance and reduce their power consumption as downward scaling continues [3]. On the other hand, scaling interconnects result in the shrinking of their cross-sectional areas, leading to a surge in resistivity as the electrons moving through the interconnect conductor experience increased scattering at the grain boundaries and surfaces of the conductor in the interconnect structure [4–8]. Also, reducing the interconnect dimensions results in an increase in the contact resistance as the electrons encounter smaller bottlenecks at the contacts. Therefore, the combined effect of increases in resistivity and contact resistance in the interconnects leads to higher resistance with downward scaling.

The performance metric of the interconnect is denoted by the delay time  $\tau$  experienced by an electrical signal traveling through it, which is expressed as  $\tau = RC$ , where R = total equivalent resistance of interconnect lines, and C = total equivalent capacitance resulting from the interconnect lines and surrounding interlayer dielectrics (ILD) [9, 10]. A manufacturable W interconnect structure requires a TiN adhesion layer for the W deposit and for the structure to remain intact through the chemical mechanical polishing (CMP) step, as well as a W nucleation layer to facilitate low-resistivity bulk W growth and to prevent TiN etching by F radicals from the

$WF_6$  precursor [11–14]. On the other hand, a manufacturable Cu interconnect structure comprises of a TaN/Ta barrier layer to prevent Cu diffusion in the ILD [15–17], and a seed layer of physical-vapor-deposited (PVD) Cu to provide nucleation for the subsequent electro-deposition to fill the Cu in the interconnect structure [18, 19]. The addition of these relatively high resistivity liners in either case results in a reduction of the total available volume for the conductor to fill the interconnect structure and hence increases the total resistance and  $\tau$ . To offset this increase, the ILD with a lower dielectric constant k is employed in the interconnect structure to reduce the total capacitance. Even with such dielectric engineering, for a 90 nm node the transistor gate delay is 2.5 ps, while a Cu/low-k interconnect delay is 10 ps [3]. Therefore, the circuit performance is limited by that of the interconnects and not by the transistors [3]. As the current technology is well beyond the 90 nm node and approaching the sub-10 nm regime, the increase in Cu resistance continues to degrade the overall circuit performance.

With the continued downward scaling of interconnect dimensions, the conductor cross-sectional area is reduced, resulting in an increase in current density. Thus, the reliability of interconnects and their ability to withstand operating current densities for a particular node size is diminished [2]. Once the current density in an interconnect line exceeds the maximum current-carrying capacity  $J_{\text{max}}$  of the conductor, the material fails due to the displacement of atoms along the path of electrons, resulting in voids, and such a mechanism is known as electromigration. The  $J_{\text{max}}$  of Cu is 2.5 MA cm<sup>-2</sup> [20] and  $1 \,\mathrm{MA\,cm}^{-2}$  for W [21, 22]. In order to extend the  $J_{\text{max}}$  for Cu and W, material engineering approaches such as stress engineering and capping are employed [2]. To implement such approaches, the Blech length [23–25], or the maximum length of the interconnect line at which the internal stress in the conductor can offset electromigration, is experimentally determined. Interconnect lines are then designed for lengths shorter than the Blech length [24, 26, 27] to prevent electromigration. In addition, capping layers are employed to cover the interconnect lines so that the conformal coating of such layers can provide an adhesive force for the conductor to counter electromigration. Combining these two approaches, the  $J_{\text{max}}$  of Cu can be extended to 3 MA cm<sup>-2</sup> [2]; however, the current density for 10 nm nodes and beyond is expected to be well above this figure [2]. Therefore, it is critical to explore and evaluate alternative conductors to replace Cu and W for interconnects in order to meet both the performance and reliability requirements of advanced nodes.

In order to evaluate the candidates for replacing Cu and W in the interconnects of advanced nodes, materials with different electron mean free paths are considered, since Cu and W are susceptible to resistivity surges due to the increased electron scattering for nanoscale linewidths [28]. One approach is to identify conductors with an electron mean free path in the bulk that is much smaller than those of Cu and W. Such materials have higher bulk resistivities compared to Cu and W due to more electron–electron scattering. However, as these materials are scaled down to the nanoscale, surface scattering becomes the dominant contributor to resistivity

[28]. Thus, they may exhibit resistivity comparable to Cu and W in the nanoscale regime. One example is NiSi, with an electron mean free path of ~5 nm [29, 30], compared to 40 nm for Cu [31]. NiSi was reported to have a resistivity of 19  $\mu\Omega$  cm for <30 nm linewidths—about four times that of Cu—and a significantly higher  $J_{\rm max}$  of 10 MA cm<sup>-2</sup> [30]. However, control of monosilicide phase formation throughout the conductor length is a major challenge in functionalizing NiSi interconnects.

Another approach is to identify materials with an electron mean free path that is much longer than those for Cu and W. For such materials, only interface scattering contributes to resistance because the electrons experience near-ballistic transport at sub-100 nm dimensions. An example is the multiwalled CNT (MWCNT) which can have an electron mean free path of up to 1  $\mu$ m [32–34], as well as a  $J_{\rm max}$  on the order of 100 MA cm<sup>-2</sup> [35–39] due to its strong sp<sup>2</sup> C–C bonds. Because of its exceptionally high  $J_{\rm max}$  and the potential of CNT-based nanostructures to achieve resistance comparable to or lower than their Cu and W counterparts, the CNT is the leading candidate to replace Cu and W in interconnect vias and contacts.

An MWCNT is made up of concentric cylinders, each one being a rolled-up sheet of graphene. Thus, its two ends exhibit unsaturated carbon bonds from each graphene sheet or shell suitable for making stable and low-resistance contacts. The two most common ways of growing CNTs in an interconnect via structure are by plasma-enhanced chemical vapor deposition (PECVD) and thermal CVD, both consisting of the catalytic decomposition of hydrocarbons on dewetted catalyst sites [40]. While PECVD utilizes plasma to maintain the vertical alignment of CNTs, for thermal CVD the alignment of the densely packed CNT is achieved with van der Waals forces among the neighboring CNTs [41]. Extensive experiments have conclusively demonstrated that growth temperatures in the 800 °C-1100 °C range lead to long-range order in CNTs and fewer defects [42], thus ensuring long electron mean free paths. In recent years, the CNT has been evaluated as a via material with various experimental foci, one being to integrate them into vias with a growth temperature of ~400 °C, compatible with a back-end-of-line thermal budget [43]. In particular, Katagiri [44–46] reported CNT vias 70 nm wide with an aspect ratio ~1, while Vollebregt [47] characterized CNT vias with a linewidth in the 1-4  $\mu$ m range. However, further study is needed for sub-100 nm linewidths to ensure that the structures containing low-temperature CNTs meet the performance and reliability requirements. Chiodarelli [48] described a catalyst engineering scheme to reduce via resistance by increasing the CNT packing density inside vias, at a CNT growth temperature of 550 °C. However, the test device reported comprised of 300 nm vias without projections for smaller linewidths. On the other hand, Zhou [49] reported CNT via results for linewidths down to 60 nm and projected the resistance for a 30 nm via. Van der Veen [31] reported an electron mean free path for CNT approaching that of Cu in 150 nm vias. Graham [50] succeeded in fabricating a 30 nm CNT via with CNTs grown at 700 °C and further annealed to 850 °C during electrical measurement, but the reported via

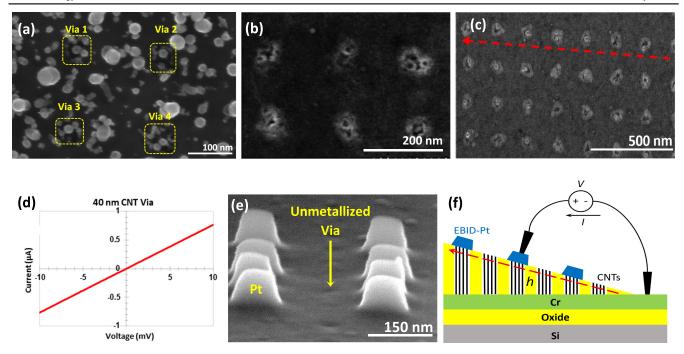

Figure 1. (a) Top-view SEM images of 40 nm vias after CNT growth. (b) CNT vias of 40 nm after  $Al_2O_3$  filling and polishing. (c) Top-view of wedge formed after polishing and before EBID-Pt deposition. The arrow indicates the direction of the wedge from low to high. (d) Typical measured I-V behavior that yields via resistance  $R_{via}$  before EBID-Pt top-contact metallization. (e) Glancing view of CNT vias after EBID-Pt. Alternate vias are selectively metallized in order to avoid overlaps. (f) Cross-sectional schematic of wedge with nanoprobing setup showing varying via height h used for contact resistance extraction. The arrow indicates the direction of the wedge as in (c). (g) Cross-sectional TEM images of a row of 40 nm CNT vias with EBID-Pt top contacts, confirming that the lateral spread of the deposited Pt is limited to one via. The inset shows a stray a-C deposited on the field due to the organometallic precursor used in the EBID process. (h) High-resolution TEM image of a 40 nm via revealing a CNT with a diameter of  $\sim$ 5 nm.

resistance was two orders of magnitude higher than its Cu and W counterparts.

All of the above findings, while providing useful knowledge for further studies toward the realization of CNT vias, nevertheless share one common challenge: namely, controlling and minimizing the resistance between the CNT and the metal contacts to achieve an interconnect via resistance approaching that of Cu and W. Furthermore, the effect of via contact engineering on reliability as well as performance has not been addressed thus far. In this paper, we present a study to correlate CNT contact resistance with both the performance and reliability of 60 nm and 40 nm vias. We also examine the prospects of contact engineering in maintaining the CNT's superiority in reliability over all other materials, while continuing to improve its performance to approach that of Cu and W, in the quest to be the interconnect material for end-of-roadmap semiconductor technology nodes.

#### 2. Device fabrication and characterization

Via structures with  $60 \text{ nm} \times 60 \text{ nm}$  and  $40 \text{ nm} \times 40 \text{ nm}$  cross-sections and 130 nm and 80 nm heights, respectively, are patterned using electron-beam (e-beam) lithography and reactive ion etching, as previously reported [49]. In order to enable the catalyst-assisted PECVD tip-growth of the CNTs inside the vias, a 3 nm Ni blanket deposition is carried out using e-beam evaporation [49]. Figure 1(a) shows the top-view SEM image

of the 40 nm vias after CNT growth. As the Ni catalyst was deposited on the entire sample, this results in the growth of stray CNTs around the vias as well. To obtain the areal density, the number of CNTs in each via before dielectric filling and polishing is counted. This method takes into account all the CNT tips observed from the SEM images, some of which may not emerge from the dielectric filler upon polishing to be part of the via top-contact. Therefore, this method provides an upper limit for the CNT areal density. The as-grown CNT areal density obtained in a  $40 \, \text{nm} \times 40 \, \text{nm}$  via is  $\sim 10^{12} \, \text{cm}^{-2}$ . To prepare vias for subsequent top-contact metallization, it is necessary to fill the interstices inside each via to avoid the shorting of the top and bottom contacts. To achieve this, a 6 nm conformal Al<sub>2</sub>O<sub>3</sub> film using atomic layer deposition is used. The sample is then subjected to mechanical polishing using SiO<sub>2</sub> nanoparticle slurry to make contact with the sample at an angle in order to fashion a  $\sim 1^{\circ}$  wedge on the surface. The topview SEM images of a few vias after polishing, and of the resulting wedge are shown in figures 1(b) and (c), respectively. Such a wedge allows one to measure vias with different heights on the same sample and extract contact resistance, with all the devices grown under the same process conditions, thus minimizing process variations. An area of Cr underlayer is exposed near the wedge using a focused ion beam (FIB) that serves as the ground for the measurement. To ensure that the oxide coating on the CNTs is removed and the CNT shells are exposed after polishing, a preliminary test is performed on a few vias with a typical I-V behavior shown in figure 1(d),

Figure 1. (Continued.)

confirming ohmic conduction. The corresponding resistance of  $13 \, \mathrm{k}\Omega$  for this 40 nm via falls within the range projected from measurements on CNT vias with widths ranging from 150 nm to 60 nm that were fabricated using similar process conditions [49].

To reduce measurement variations among the vias and to improve the CNT-metal contact, the via top-contacts are metallized for each of the five different via heights using the electron-beam-induced deposition (EBID) of Pt in an SEM chamber. EBID enables us to selectively deposit Pt on top of the vias without any additional masking steps. Deposits with fine control can be made using EBID with no damage to the

substrate, unlike using a focused ion beam (FIB), which generally creates defects and Ga contamination [51]. For EBID, a base pressure of  $10^{-3}$  Pa is reached before the Pt precursor, trimethyl(methylcyclopentadienyl)platinum(IV), is introduced using a gas injection system (GIS). An advantage of using a non-halide precursor is that it does not lead to substrate damage from the dissociated halide radicals. Prior to Pt deposition, the sample is placed in the chamber for an hour to allow outgassing to occur. This step is critical in ensuring that oxide-free depositions are made on the vias. The chamber is then subjected to plasma cleaning to purge potential contaminants on the chamber walls, especially a-C, and to clean

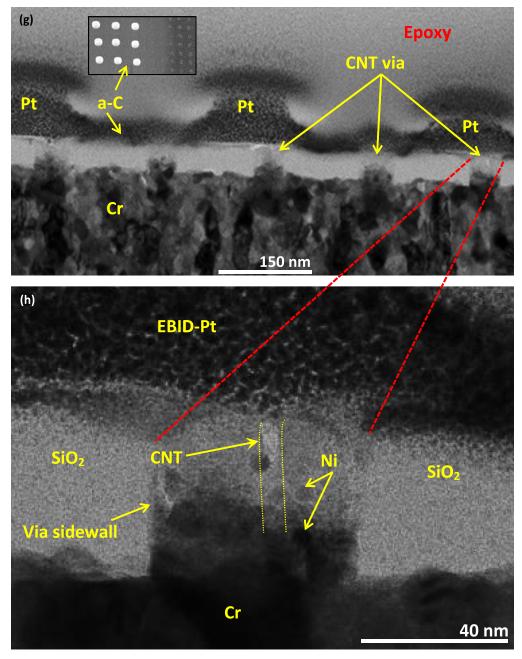

**Figure 2.** Measured via resistance versus via height for 40 nm CNT vias. Statistical linear fitting of the data yields the *average* contact resistance  $R_{\rm C}$  from the  $R_{\rm via}$  intercept. The inset shows the mean and standard deviation of measured resistances for each via height with  $R^2 = 0.91$ . The data further supports ohmic transport through the entire via structure.

the sample surface to further expose the CNT tips. The cleaning efficiency can be checked by using an irradiating e-beam on the sample for 5 min to ensure no a-C remains.

For EBID, the working distance is set at 10 mm and the accelerating voltage at 10 kV, with an emission current of 80 pA. The Pt precursor is delivered from the GIS through a needle outlet which is kept at  $3 \sim 4 \,\mathrm{mm}$  from the sample surface. The e-beam dissociates the precursor molecules and yields Pt deposition on the impinged spot (via) on the sample surface. The lateral beam spread causes the deposit to be somewhat larger than the targeted spot. The beam raster time on each via is 1 s for a 90 nm × 90 nm spot to cover a  $60 \, \text{nm} \times 60 \, \text{nm}$  via. Depositions with a longer raster time result in significantly wider lateral spreads, which can lead to deposits on the adjacent vias and skewed I-V data. Alternate vias along the same row are metallized to ensure no overlaps of Pt deposits due to lateral beam spread. Multiple vias for each height are metallized to yield sufficient data for the subsequent statistical analysis. An SEM image of two rows of metallized vias sandwiching an unmetallized one is shown is figure 1(e). A schematic for the I–V measurement of vias with metallized top contacts on the fashioned wedge is illustrated in figure 1(f).

Figure 1(g) shows a TEM cross-section of several 40 nm CNT vias along a row of the wedge. It indicates that the alternate vias are metallized and confirms that the Pt deposits do not overlap. The presence of a-C from the organometallic Pt precursor is evident but is shown to be not sufficiently conductive to create a significant conducting path between the adjacent vias. Figure 1(h) is a high-resolution TEM image of a single CNT via. The vias are designed for a horizontal cross-section of 40 nm  $\times$  40 nm, while the vertical cross-section traversed by the transmitted electron beam producing the image can be as wide as  $40\sqrt{2}$  or 57 nm. Furthermore, etching in the via patterning process can result in horizontal

cross-sections that might not be perfect squares. The fact that only one CNT is clearly visible is a result of ion milling creating a sufficiently thin sample—usually less than 50 nm thick. Thus, it is not likely that most of the CNTs observed in the top-view SEM image in figure 1(b) are present in such cross-sectional views of the very thin slice. Nevertheless, the observed CNT in figure 1(h) reveals alignment with the via sidewalls and interfaces with both the underlayer Cr and Pt top-contact, similar to findings for a 60 nm via [49].

## 3. Contact resistance and current-carrying capacity measurements

The electrical characterization of CNT vias was carried out by nanoprobing vias with metallized top-contacts, as shown schematically in figure 1(f). One nanoprobe makes contact with the Pt cap while the other rests firmly on the area of exposed Cr serving as the ground. The Cr underlayer is 300 nm thick, which ensures minimal contribution to the total via resistance. In fact, the sheet resistance of the Cr layer measured before oxide deposition is  $3.2 \Omega/\Box$ . After the initial *I–V* sweep to confirm conduction and ensure the firm mechanical contact of the nanoprobe with the Pt cap, the CNT via is subjected to current stressing starting at 1  $\mu$ A in multiple cycles, until the resistance stabilizes. This simple contact engineering technique further improves the top-contact through joule heating, as no thermal treatment is performed after EBID deposition. Significant improvement in the CNT via resistance by thermal annealing has been reported [31, 50]. In particular, Graham [50] reported a resistance drop by over two orders of magnitude with annealing up to 850 °C. In our experiment, instead of thermally annealing the entire sample, current stressing of the individual CNT vias is performed, as in horizontal CNT interconnects [51]. The resistance is recorded after each stress

cycle, and the final value is obtained when no reduction in resistance occurs with further stressing. Multiple via resistances for each of the five different via heights using the technique illustrated in figure 1(f) are plotted in figure 2.

The range of via heights is selected such that the lowest height is at least half the maximum via height in order to avoid the accidental shorting of the top and bottom electrodes. Since the via height range is 48-80 nm, as shown in figure 2, the electron free path is at most 80 nm through the CNTs inside each via. Nevertheless, the transport through the entire via structure is assumed to be ohmic, which is the basis of the ensuing analysis. Each via resistance  $R_{\rm via}$  can then be expressed as

$$R_{\text{via}} = R_{\text{m}} + R_{\text{C}} + \rho_{\text{CNT}} \times h/A_{\text{CNT}}.$$

(1)

$R_{\rm m}$  represents the total resistance contributions from the Cr underlayer, probes, and probe-Cr contacts, and its value is estimated by landing both the nanoprobes on the exposed Cr area. The typical value obtained is  $\sim 10 \Omega$ , which is < 0.2% of the lowest measured  $R_{\text{via}}$ . Hence,  $R_{\text{m}}$  can be neglected in the subsequent analysis.  $R_{\rm C}$  is the total contact resistance of the via and varies among them according to the number and diameter of the CNTs inside each via.  $A_{\text{CNT}}$  is the total CNT cross-sectional area inside the via and also varies among them. Such variations are manifested in the data spread for each via height shown in figure 2. The via height h is fixed among vias of the same height using the wedge structure shown in figure 1(f). While the CNT resistivity  $\rho_{\text{CNT}}$  depends on the number of defects in the graphitic structure and number of walls, relative to the variations of  $A_{\text{CNT}}$  and  $R_{\text{C}}$  among the vias (to be addressed in the ensuing paragraph), and considering the small range of via heights used, the variation in  $ho_{\mathrm{CNT}}$  among them is expected to be small, and an average value for the sample is assumed in the analysis. Thus, in using equation (1) to extract the contact resistance from  $R_{\text{via}}$  versus the h data, the resistance intercept of the statistical linear fit amounts to an average  $R_{\rm C}$  that takes into account all variations among the vias. The fitted line has a slope of 61  $\Omega$  nm<sup>-1</sup> with  $R^2 = 0.91$ , supporting the assumption that conduction through the entire CNT via structure is indeed ohmic, with an average CNT linear resistivity  $\rho_{\rm CNT}/A_{\rm CNT}=61~\Omega~{\rm nm}^{-1}$ . The mean  $R_{\text{via}}$  and standard deviation for each h are given in the inset in figure 2. Therefore, despite significant variations among the vias, such statistical analysis can be employed to extract an average via contact resistance and an average CNT resistivity, with  $R_{\rm C}=2.8\,{\rm k}\Omega$  and  $\rho_{\rm CNT}=1.8\,{\rm m}\Omega$  cm, where an average  $A_{\rm CNT} \sim 300 \, {\rm nm}^2$  is obtained by sampling a large number of 40 nm vias. This resistivity value is an order of magnitude lower than the ones obtained for the lower CNT growth temperature [47], but still more than two orders of magnitude higher than Cu and W with similar linewidths [11–13].

To examine the variations among vias further, a statistical analysis is performed on the variations in the diameter and number of CNTs inside each via, as well as the resulting variations in the extracted contact resistance. The diameters and number of CNTs making contacts with the top and bottom electrodes define the total conducting cross-sectional area

**Table 1.** Statistics of 40 nm CNT via parameters which contribute to variations in the measured via resistance and extracted contact resistance. For the diameter and number of CNTs, the data is obtained from the SEM images of unfilled and unpolished vias, such as figure 1(a), whereas the total CNT area in the via is obtained from the SEM images of polished samples such as figure 1(b). For each parameter, the mean  $\mu$ , standard deviation  $\sigma$ , and coefficient of the variation CV are obtained, showing similarities in the variations for  $A_{\rm CNT}$  and  $R_{\rm C}$ .

| Parameter in a set of 40 nm CNT vias                           | μ    | σ    | CV(%) |

|----------------------------------------------------------------|------|------|-------|

| CNT diameter across the entire set (nm)                        | 9.03 | 3.62 | 40.1  |

| Number of CNTs in via, $N_{\rm CNT}$                           | 16   | 2    | 12.5  |

| Total area of CNTs in via, $A_{\text{CNT}}$ (nm <sup>2</sup> ) | 310  | 101  | 32.6  |

| Extracted $R_{\rm C}$ (k $\Omega$ ) from figure 2              | 2.84 | 0.8  | 28.6  |

in a via, and variations in that area among the vias manifest themselves in variations in the measured  $R_{\rm via}$  and extracted  $R_{\rm C}$ . For the set of vias used in this experiment, the mean  $(\mu)$ , standard deviation  $(\sigma)$ , and coefficient of variation (CV) for each of these parameters are summarized in table 1.

For CNT vias exhibiting the ohmic conduction described by equation (1), both contact resistance and the total CNT resistance are inversely proportional to  $A_{\text{CNT}}$ . Thus, one would expect the extracted  $R_{\rm C}$  to have variations similar to those in  $A_{\text{CNT}}$ , as shown in table 1. If we were to use the average CNT diameter and number given in table 1 to deduce the average  $A_{\text{CNT}}$ , it would be ~1000 nm<sup>2</sup>. This value is clearly an overestimation as both the SEM and TEM images of the unpolished vias in figure 1 reveal CNTs with lengths lower than the via heights, which do not contribute to conduction. On the other hand, the presence of the oxide surrounding the vias as well as the exposed dielectric filler material in the polished sample results in insufficient contrast for accurate individual CNT diameter and number determination, but adequate for the total area estimation. The resulting  $A_{\text{CNT}}$  statistics given in table 1 match well those for  $R_{\rm C}$ , thus validating the analysis used to extract the latter.

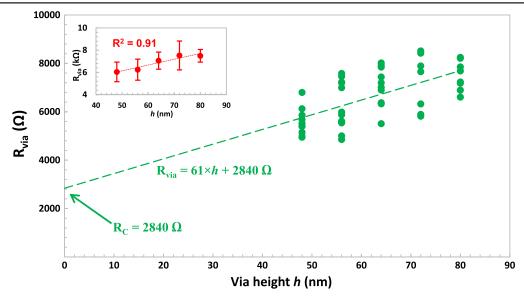

We have recently demonstrated the advantage of integrating CNTs at temperatures higher than those considered to be acceptable for IC manufacturing, where the resulting high CNT quality leads to lower resistivity and higher currentcarrying capacity [52, 53]. To obtain CNTs via current-carrying capacity  $J_{\text{CNT}}$ , two complementary methods are employed. For the first method, a constant current is applied to the via in incremental steps and the resistance is recorded after each stress cycle until device breakdown. This is similar to reports on studies for horizontal CNT interconnects [54, 55]. The resistance versus stress current behavior for 40 nm and 60 nm CNT vias with and without a Pt cap are shown in figures 3(a) and (b), respectively. It is observed that the via with the Pt top-contact can carry much higher current than the one without, with reduced via resistance. The Pt contact allows all the exposed CNT tips and the graphene shells inside each CNT to interface with the deposited metal, whereas for vias without the metallized top-contact, via resistance is very sensitive to variations in probe-via contact, which generally does not cover all the CNTs inside the via,

**Figure 3** (a) Resistance versus stress current behavior for 40 nm vias with and without EBID-Pt top-contact. Metallization and current stressing improve and stabilize the top via contact by making conformal interfaces between the metal and exposed CNT tips, resulting in lower via resistance and improved current-carrying capacity compared to unmetallized vias. (b) Resistance versus stress current behavior for 60 nm vias with and without EBID-Pt, showing the same trend as 40 nm vias.

resulting in higher contact resistance and increased joule heating from current stressing. Furthermore, heat dissipation from the CNTs under current stressing is less efficient without the top-contact metal, and hence the via breaks down at a lower current density. An additional benefit of having a metallized via is further improvement of the top-contact by joule heat from current stressing, which facilitates the fusion of nanocrystalline grains in the metal, as observed by Wilhite [51] for EBID-W contacts and reported by Wang [56] for EBID-Pt nanocrystals. Thus, current stressing allows for local annealing of the individual vias on the test structure instead of having to thermally anneal the entire sample. Study of the horizontal CNT interconnects using end-bonded contacts after CNT growth was reported by Chiodarelli [57], showing similar improvement as in the case of horizontal carbon nanofibers after contact metallization [54]. Figure 3(a) shows the resistance behavior versus stress current for a 40 nm via, with breakdown at 1 mA. Using the average  $A_{\rm CNT} \sim 300~{\rm nm}^2$  obtained for 40 nm vias,  $J_{\rm CNT} \sim 330~{\rm MA~cm}^{-2}$ . For the 60 nm via data in figure 3(b), with an average  $A_{\rm CNT} \sim 700~{\rm nm}^2$ ,  $J_{\rm CNT} \sim 170~{\rm MA~cm}^{-2}$ . These via current-carrying capacities are more than two orders of magnitude higher than the  $J_{\rm max}$  for Cu and W and are consistent with the reported values [11–13]. Table 2 summarizes the results obtained for 40 nm and 60 nm vias with and without top-contact metallization. The improvements in both via resistance and current-carrying capacity are evident for each linewidth.

The breakdown in CNTs tends to occur at defect sites [58] and can be exacerbated by ambient oxygen adsorption [59]. Therefore, the improvement of long-range order in CNTs by reducing defects and using non-oxide-based dielectric fillers can result in further enhancement in  $J_{\rm CNT}$  as well as a reduction in via resistance. Nonetheless, the  $J_{\rm CNT}$  values obtained in this experiment and reported by others are

**Table 2.** Resistance and current-carrying capacity of 40 and 60 nm vias with and without Pt top-contacts. EBID metallization stabilizes the top-contact and results in lower resistance and higher current-carrying capacity.

| Via dimensions, width (nm) × height (nm) | Contact metal | Resistance (k $\Omega$ ) | Current-carrying capacity (MA cm <sup>-2</sup> ) | CNT areal density (# cm <sup>-2</sup> ) |

|------------------------------------------|---------------|--------------------------|--------------------------------------------------|-----------------------------------------|

| 40 × 80                                  | none          | 18                       | 14                                               | ~10 <sup>12</sup>                       |

| $40 \times 80$                           | none          | 19                       | 14                                               |                                         |

| $40 \times 80$                           | EBID Pt       | 6.1                      | 330                                              |                                         |

| $40 \times 80$                           | EBID Pt       | 6.8                      | 330                                              |                                         |

| $60 \times 130$                          | none          | 25                       | 10                                               | $\sim 3 \times 10^{11}$                 |

| $60 \times 130$                          | none          | 15                       | 17                                               |                                         |

| $60 \times 130$                          | EBID Pt       | 1.4                      | 170                                              |                                         |

| $60 \times 130$                          | EBID Pt       | 1.7                      | 170                                              |                                         |

| $60 \times 130$                          | EBID Pt       | 1.4                      | 170                                              |                                         |

| $60 \times 130$                          | EBID Pt       | 2.0                      | 170                                              |                                         |

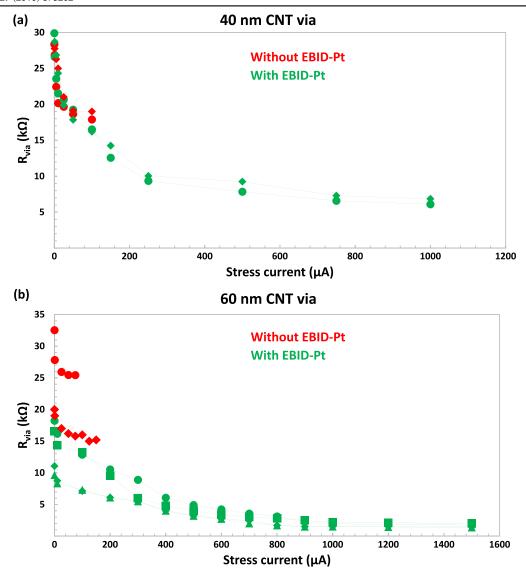

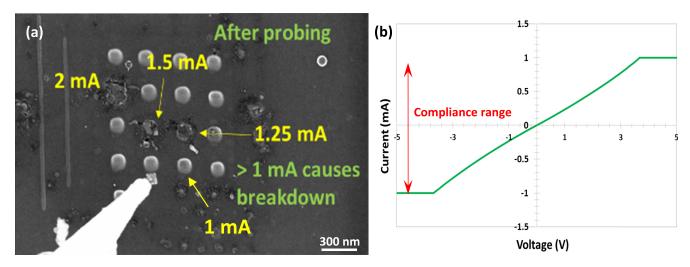

**Figure 4.** (a) SEM image of CNT vias after voltage sweep test. Different current ranges are used to reveal the via current capacity. Only the device with a current compliance range of  $\pm 1$  mA remains intact and those with higher compliance ranges break down, confirming the measured current-carrying capacity of 330 MA cm<sup>-2</sup>. (b) I-V sweep with current capped at  $\pm 1$  mA.

more than sufficient for functionalized on-chip CNT interconnects to last through to the end of semiconductor technology nodes, if the line resistance can be reduced to approach its Cu and W counterparts. While the resistance reductions by contact metallization and similar improvements from higher CNT areal density given in table 2 are encouraging, the resistance values are still too high for integration into future technology nodes.

In order to verify the current-carrying capacity of the CNT vias obtained, a second test is conducted to determine the inherent current-carrying capacity of the CNT via without using a constant stress current. The voltage across each via is swept between a pre-defined or compliance range of currents. If a continuous linear I-V is obtained, it implies that the CNTs inside the via remain intact. An array of Pt-metallized vias after the voltage sweep is shown in figure 4(a). At the outset, a current compliance range of  $\pm 1$  mA is used with a voltage sweep from -4 V to 4 V. As shown in figure 4(b), continuous I-V behavior is obtained for this compliance range. The via meeting this compliance remains intact, while those with higher compliance ranges break down as shown in figure 4(a).

Thus, the current-carrying capacity shown in figure 3(a) is verified.

Finally, it is important to know how the latest results for CNT vias compare with the vias made of the conventional materials, Cu and W, with similar dimensions, and with pertinent results reported by others. A comparison of the  $R_{via}$ and  $J_{\text{CNT}}$  of CNT, Cu, and W vias with similar dimensions is given in table 3. It is clear how the CNT areal density correlates with the current-carrying capacity. However, in order to achieve higher areal density, smaller CNT diameters are needed to pack more of them into a via, which could increase the overall via resistance. Also, defects in CNTs can limit the via current-carrying capacity. It was reported that even for 700 °C growth, the defect ratio  $(I_D/I_G)$  from Raman analysis was 0.85 [52, 53]. Therefore, taller vias are susceptible to reduced current-carrying capacity as more defects are present along the CNT length, consistent with the data obtained in this work, given in table 3. Furthermore, similar to the findings on horizontal CNT interconnects [60], the dissipation of joule heat from current stressing is less efficient for a taller via, contributing to the variations in the  $J_{\text{CNT}}$  among vias with different heights. Katagiri [44, 45] reported a resistance of

**Table 3.** A comparison of electrical characteristics among CNT, Cu, and vias. CNT vias clearly show superior current-carrying capacities but inferior resistance—the key challenge for CNTs in replacing Cu and W in on-chip interconnects for end-of-roadmap technology nodes.

|              | Via dimensions<br>(width × height) | CNT growth temperature (°C) | $R_{\mathrm{via}}$ (k $\Omega$ ) | $J_{ m CNT}$ (MA cm <sup>-2</sup> ) | CNT areal density<br>(# cm <sup>-2</sup> ) | Average CNT diameter (nm) |

|--------------|------------------------------------|-----------------------------|----------------------------------|-------------------------------------|--------------------------------------------|---------------------------|

| This work    | 40 nm × 80 nm                      | 700                         | 6.1                              | 330                                 | 10 <sup>12</sup>                           | 9                         |

|              | $60\mathrm{nm}	imes130\mathrm{nm}$ | 700                         | 1.7                              | 170                                 | $3 \times 10^{11}$                         | 20                        |

| Ref [50]     | $30\mathrm{nm}	imes150\mathrm{nm}$ | 700                         | 7.8                              | 400                                 | $1.5 \times 10^{11}$                       | 15                        |

| Ref [44, 45] | $70\mathrm{nm}	imes100\mathrm{nm}$ | 450                         | 11                               | 100                                 | $5 \times 10^{11}$                         | 10                        |

| Cu [11]      | $30\mathrm{nm}	imes130\mathrm{nm}$ | NA                          | 0.025                            | 2.5                                 | NA                                         | NA                        |

| W [12, 13]   | $30\text{nm}\times130\text{nm}$    | NA                          | 0.060                            | 1                                   | NA                                         | NA                        |

11 k $\Omega$  and a current-carrying capacity of 100 MA cm<sup>-2</sup> for a 70 nm via with CNT growth at 450 °C, while an extensive study by Vollebregt [61] conclusively demonstrated that the number of defects in CNTs increases as the growth temperature is reduced. Graham [50] reported that 700 °C CNT growth and subsequent annealing resulted in a current-carrying capacity of 400 MA cm<sup>-2</sup> for a 30 nm via with a CNT areal density of  $1.5 \times 10^{11}$  cm<sup>-2</sup>. This reported higher  $J_{\rm CNT}$  is probably due to a multi-walled structure with a hollow interior, as evident in the cross-sectional TEM image of a CNT in [50], whereas the CNTs in our vias mostly have a 'bamboo' structure, where interlayer defects can lower their  $J_{\text{max}}$  [55, 61–63]. In all cases, while the current-carrying capacities well exceed those projected for end-of-roadmap technology nodes, via resistance and the replacement of Cu and W remain challenges, though our results suggest that further innovations in contact engineering could begin to overcome them.

#### 4. Conclusion

CNT vias with  $40 \, \text{nm} \times 40 \, \text{nm}$  and  $60 \, \text{nm} \times 60 \, \text{nm}$  crosssections have been fabricated and characterized to determine the via nanostructure, contact resistance, CNT resistivity, and current-carrying capacity. The contact resistance of 40 nm CNT vias has been extracted and is shown to have a similar statistical variation among vias as the total CNT area inside the via,  $A_{\text{CNT}}$ . Therefore, further contact engineering is needed to control and enhance  $A_{\text{CNT}}$  to reduce the contact resistance as well as to improve or at least maintain the via current-carrying capacity  $J_{\rm CNT}$ . For 40 nm and 60 nm CNT vias,  $J_{\text{CNT}}$  is more than two orders of magnitude higher than Cu and W, making it a viable candidate for further development towards the functionalization of CNT interconnects. However, the via resistances reported here and by others are two orders of magnitude higher than their Cu and W counterparts. Our scheme for contact engineering suggests that further innovations in contact improvement could lead to a corresponding improvement in CNT via performance, while preserving the superiority of high current-carrying capacity to all other potential replacements for Cu and W.

#### References

- [1] Moore G E 1998 Cramming more components onto integrated circuits *Proc. IEEE* **86** 82–5

- [2] International Technology Roadmap for Semiconductors 2013 edn (www.itrs2.net)

- [3] Sun S C 1997 Process technologies for advanced metallization and interconnect systems Int. Electron Devices Meeting pp 765–8

- [4] Steinlesberger G, Engelhardt M, Schindler G, Steinhogl W, von Glasow A, Mosig K and Bertagnolli E 2002 Electrical assessment of copper damascene interconnects down to sub-50 nm feature sizes *Microelectron. Eng.* 64 409–16

- [5] Steinhogl W, Steinlesberger G, Perrin M, Scheinbacher G, Schindler G, Traving M and Engelhardt M 2005 Tungsten interconnects in the nano-scale regime *Microelectron. Eng.* 82 266–72

- [6] Steinhogl W, Schindler G, Steinlesberger G, Traving M and Engelhardt M 2005 Comprehensive study of the resistivity of copper wires with lateral dimensions of 100 nm and smaller J. Appl. Phys. 97 023706

- [7] Steinhogl W, Schindler G, Steinlesberger G and Engelhardt M 2002 Size-dependent resistivity of metallic wires in the mesoscopic range *Phys. Rev.* B 66 075414

- [8] Schindler G, Steinlesberger G, Engelhardt M and Steinhogl W 2003 Electrical characterization of copper interconnects with end-of-roadmap feature sizes Solid-State Electron. 47 1233–6

- [9] Rosenberg R, Edelstein D C, Hu C K and Rodbell K P 2000 Copper metallization for high performance silicon technology *Annual Review of Materials Science* 30 229–62

- [10] Chen F and Shinosky M 2009 Addressing Cu/low-k dielectric TDDB-reliability challenges for advanced CMOS technologies IEEE Trans. Electron Devices 56 2–12

- [11] Haimson S, Shacham-Diamand Y, Horvitz D and Rozenblat A 2012 Resistivity monitoring of the early stages of W CVD nucleation for sub-45 nm process *Microelectron. Eng.* 92 134–6

- [12] Herner S B, Desai S A, Mak A and Ghanayem S G 1999 Homogeneous tungsten chemical vapor deposition on silane pretreated titanium nitride *Electrochemical and Solid State* Letters 2 398–400

- [13] Lee P I, Cronin J and Kaanta C 1989 Chemical vapor deposition of tungsten (CVD W) as submicron interconnection and via stud *J. Electrochem. Soc.* 136 2108–12

- Hillman J, Foster R, Faguet J, Triggs W, Arora R, Ameen M, Martin F and Arena C 1995 Integrated Cvd titanium and titanium nitride processes for sub-0.5 μm metallization Solid State Technol. 38 147–51

- [14] Peng Y C, Chen L J, Hsieh W Y, Yang Y R and Hsieh Y F 1998 Structural and electrical properties of chemical vapor deposition tungsten overgrowth on physical vapor deposited

- and metalorganic chemical vapor deposited TiN adhesion layers *J. of Vacuum Science & Technology* B **16** 2013–8

- [15] Chang C C, Chen J S and Hsu W S 2004 Failure mechanism of amorphous and crystalline Ta-N films in the Cu/Ta-N/Ta/ SiO<sub>2</sub> structure J. Electrochem. Soc. 151 G746–50

- [16] Gerlich L, Ohsiek S, Klein C, Geiss M, Friedemann M, Kucher P and Schmeisser D 2013 Interface engineering for the TaN/Ta barrier film deposition process to control Tacrystal growth, *Microelectron. Eng.* 106 63–8

- [17] Hubner R, Hecker M, Mattern N, Hoffmann V, Wetzig K, Wenger C, Engelmann H J, Wenzel C, Zschech E and Bartha J W 2003 Structure and thermal stability of graded Ta-TaN diffusion barriers between Cu and SiO<sub>2</sub> Thin Solid Films 437 248–56

- [18] Bruning R, Muir B, McCalla E, Lempereur E, Bruning F and Etzkorn J 2011 Strain in electroless copper films monitored by x-ray diffraction during and after deposition and its dependence on bath chemistry *Thin Solid Films* 519 4377–83

- [19] Brunoldi G, Guerrieri S, Alberici S G, Ravizza E, Tallarida G, Wiemer C and Marangon T 2005 Self-annealing and aging effect characterization on copper seed thin films *Microelectron. Eng.* 82 289–95

- [20] Adelmann C, Wen L G, Peter A P, Siew Y K, Croes K, Swerts J, Popovici M, Sankaran K, Pourtois G and Van Elshocht S 2014 Alternative metals for advanced interconnects *IEEE Int. Interconnect Technology Conf.* pp 173–6

- [21] Walls J A 1995 Stress-voiding in tungsten-plug interconnect systems induced by high-temperature processing *IEEE* Electron Device Lett. 16 430–2

- [22] Walls J A 1997 The influence of TiN ARC thickness on stressinduced void formation in tungsten-plug vias *IEEE Trans*. *Electron Devices* 44 2213–9

- [23] Ogawa E T et al 2001 Direct observation of a critical length effect in dual-damascene Cu/oxide interconnects Appl. Phys. Lett. 78 2652–4

- [24] Chai Y, Chan P C H, Fu Y Y, Chuang Y C and Liu C Y 2008 Electromigration studies of Cu/carbon nanotube composite interconnects using Blech structure *IEEE Electron Device Lett.* 29 1001–3

- [25] Proost J, Delaey L, D'Haen J and Maex K 2002 Plasticity of electromigration-induced hillocking and its effect on the critical length J. Appl. Phys. 91 9108–15

- [26] Wang P C and Filippi R G 2001 Electromigration threshold in copper interconnects Appl. Phys. Lett. 78 3598–600

- [27] Ogawa E T, Lee K D, Matsuhashi H, Ho P S, Blaschke V A and Havemann R H 2002 Reliability and early failure in Cu/oxide dual-damascene interconnects J. Electron. Mater. 31 1052–8

- [28] Clarke J S, Jezewski C, Caro A M, Michalak D and Torres J 2014 Process technology scaling in an increasingly interconnect-dominated world Symp. on VLSI Technology pp 1–2

- [29] Wu Y, Xiang J, Yang C, Lu W and Lieber C M 2004 Singlecrystal metallic nanowires and metal/semiconductor nanowire heterostructures *Nature* 430 61–5

- [30] Lee C Y, Lu M P, Liao K F, Lee W F, Huang C T, Chen S Y and Chen L J 2009 Free-standing single-crystal NiSi2 nanowires with excellent electrical transport and field emission properties J. Phys. Chem. C 113 2286–9

- [31] van der Veen M H, Barbarin Y, Kashiwagi Y and Tokei Z 2014 Electron mean-free path for CNT in vertical interconnects approaches Cu IEEE Interconnect Technology Conf./Advanced Metallization Conf. pp 181–4

- [32] Berger C, Poncharal P, Yi Y and de Heer W 2003 Ballistic conduction in multiwalled carbon nanotubes J. Nanosci. and Nanotechnol. 3 171–7

- [33] Mann D, Javey A, Kong J, Wang Q and Dai H J 2003 Ballistic transport in metallic nanotubes with reliable Pd ohmic contacts *Nano Lett.* 3 1541–4

- [34] White C T and Todorov T N 1998 Carbon nanotubes as long ballistic conductors *Nature* 393 240–2

- [35] Feng Y and Burkett S L 2015 Fabrication and electrical performance of through silicon via interconnects filled with a copper/carbon nanotube composite *J. Vacuum Sci. Technol.* B 33 022004

- [36] Subramaniam C, Yamada T, Kobashi K, Sekiguchi A, Futaba D N, Yumura M and Hata K 2013 One-hundred-fold increase in current carrying capacity in a carbon nanotubecopper composite *Nat. Commun.* 4 2202–7

- [37] Moon S et al 2007 Current-carrying capacity of double-wall carbon nanotubes Nanotechnology 18 235201

- [38] Wei B Q, Vajtai R and Ajayan P M 2001 Reliability and current carrying capacity of carbon nanotubes Appl. Phys. Lett. 79 1172–4

- [39] Anantram M P 2000 Current-carrying capacity of carbon nanotubes *Phys. Rev.* B 62 R4837–40

- [40] Meyyappan M 2009 A review of plasma enhanced chemical vapour deposition of carbon nanotubes J. Phys. D: Appl. Phys. 42 213001

- [41] Na N, Kim D Y, So Y-G, Ikuhara Y and Noda S 2015 Simple and engineered process yielding carbon nanotube arrays with  $1.2\times10~13~\text{cm}^{-2}$  wall density on conductive underlayer at 400 °C *Carbon* **81** 773–81

- [42] Chakraborty A K, Jacobs J, Anderson C, Roberts C J and Hunt M R C 2006 Chemical vapor deposition growth of carbon nanotubes on Si substrates using Fe catalyst: What happens at the nanotube/Fe/Si interface *J. Appl. Phys.* 100 084321

- [43] Awano Y, Sato S, Nihei M, Sakai T, Ohno Y and Mizutani T 2010 Carbon nanotubes for VLSI: interconnect and transistor applications *Proc. IEEE* 98 2015–31

- [44] Katagiri M, Sakuma N, Yamazaki Y, Suzuki M, Sato S, Nihei M, Sakai T and Awano Y 2009 Low-temperature growth of multiwalled carbon nanotubes by surface-wave plasma-enhanced chemical vapor deposition using catalyst nanoparticles *Japan. J. Appl. Phys.* 48 090205

- [45] Katagiri M, Yamazaki Y, Sakuma N, Suzuki M, Sakai T, Wada M, Nakamura N, Matsunaga N, Sato S and Nihei M 2009 Fabrication of 70 nm-diameter carbon nanotube via interconnects by remote plasma-enhanced chemical vapor deposition and their electrical properties *IEEE Int. Interconnect Technology Conf.* pp 44–6

- [46] Katagiri M et al 2011 Improvement in electrical properties of carbon nanotube via interconnects Japan. J. Appl. Phys. 50 05EF01

- [47] Vollebregt S, Tichelaar F D, Schellevis H, Beenakker C I M and Ishihara R 2014 Carbon nanotube vertical interconnects fabricated at temperatures as low as 350 degrees C Carbon 71 249–56

- [48] Chiodarelli N et al 2011 Measuring the electrical resistivity and contact resistance of vertical carbon nanotube bundles for application as interconnects Nanotechnology 22 085302

- [49] Zhou C J, Vyas A A, Wilhite P, Wang P, Chan M S and Yang C Y 2015 Resistance determination for sub-100 nm carbon nanotube vias IEEE Electron Device Lett. 36 71–3

- [50] Graham A P et al 2005 How do carbon nanotubes fit into the semiconductor roadmap? Appl. Phys. A: Mat. Sci. Process. 80 1141–51

- [51] Wilhite P, Uh H S, Kanzaki N, Wang P, Vyas A, Maeda S, Yamada T and Yang C Y 2014 Electron-beam and ionbeam-induced deposited tungsten contacts for carbon nanofiber interconnects *Nanotechnology* 25 375702

- [52] Vyas A, Zhou C, Wilhite P, Wang P and Yang C Y 2016 Electrical properties of carbon nanotube via interconnects

- for 30 nm linewidth and beyond *Microelectronics Reliability* **61** 35–42

- [53] Vyas A, Yang C, Wang P, Zhou C and Chai Y 2016 Contact resistance and reliability of 40 nm carbon nanotube vias Proc. of IEEE Int. Interconnect Technology Conf. (San Jose, CA)

- [54] Saito T, Yamada T, Fabris D, Kitsuki H, Wilhite P, Suzuki M and Yang C Y 2008 Improved contact for thermal and electrical transport in carbon nanofiber interconnects *Appl. Phys. Lett.* 93 102108

- [55] Wilhite P, Vyas A A, Tan J, Tan J, Yamada T, Wang P, Park J and Yang C Y 2014 Metal–nanocarbon contacts Semicond. Sci. Technol. 29 054006

- [56] Wang Z L, Petroski J M, Green T C and El-Sayed M A 1998 Shape transformation and surface melting of cubic and tetrahedral platinum nanocrystals *The J. of Physical Chemistry* B 102 6145–51

- [57] Chiodarelli N, Fournier A and Dijon J 2013 Impact of the contact's geometry on the line resistivity of carbon nanotubes bundles for applications as horizontal interconnects Appl. Phys. Lett. 103 053115

- [58] Collins P G, Hersam M, Arnold M, Martel R and Avouris P 2001 Current saturation and electrical breakdown in

- multiwalled carbon nanotubes *Phys. Rev. Lett.* **86** 3128–31

- [59] Maeda S, Wilhite P, Kanzaki N, Yamada T and Yang C Y 2011 Change in carbon nanofiber resistance from ambient to vacuum AIP Advances 1 022102

- [60] Kitsuki H, Yamada T, Fabris D, Jameson J R, Wilhite P, Suzuki M and Yang C Y 2008 Length dependence of current-induced breakdown in carbon nanofiber interconnects Appl. Phys. Lett. 92 173110

- [61] Vollebregt S, Ishihara R, Tichelaar F D, Hou Y and Beenakker C I M 2012 Influence of the growth temperature on the first and second-order Raman band ratios and widths of carbon nanotubes and fibers Carbon 50 3542–54

- [62] Cassell A M, Ye Q, Cruden B A, Li J, Sarrazin P C, Ng H T, Han J and Meyyappan M 2003 Combinatorial chips for optimizing the growth and integration of carbon nanofibre based devices *Nanotechnology* 15 9–15

- [63] Melechko A V, Klein K L, Fowlkes J D, Hensley D K, Merkulov I A, McKnight T E, Rack P D, Horton J A and Simpson M L 2007 Control of carbon nanostructure: from nanofiber toward nanotube and back J. Appl. Phys. 102 074314